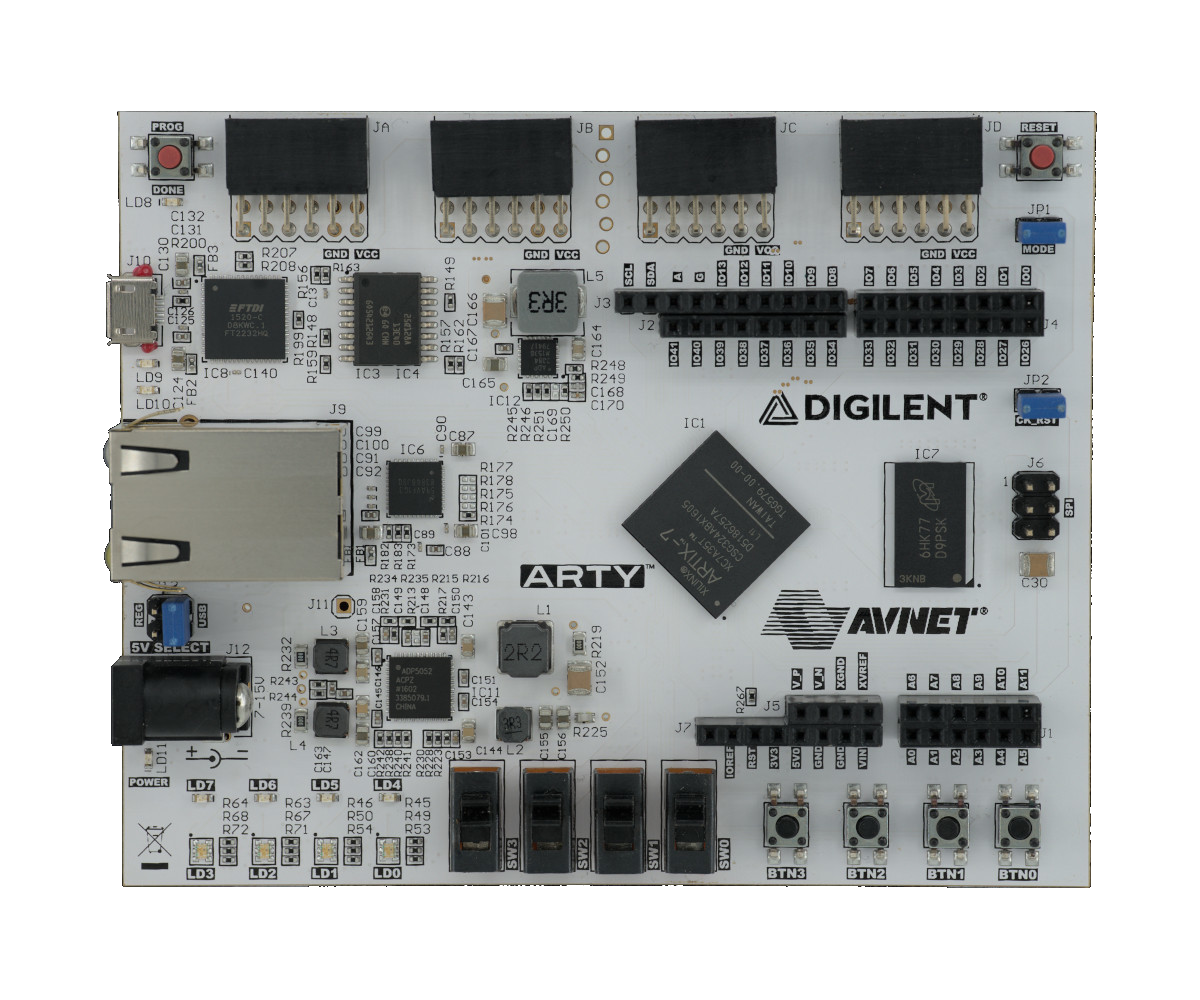

Arty-A7 board¶

The Arty-A7 board allows testing its on-board DDR3 module. The board is designed around the Artix-7 Field Programmable Gate Array (FPGA) from AMD(Xilinx).

Fig. 13 Arty-A7 board¶

The following instructions explain how to set up the board. For FPGA digital design documentation for this board, refer to the Digital design chapter.

Board configuration¶

Connect the board USB and Ethernet cables to your computer and configure the network. The bitstream will be loaded from flash memory upon device power-on or after pressing the PROG button.

Last update:

2026-03-07