PCIe support¶

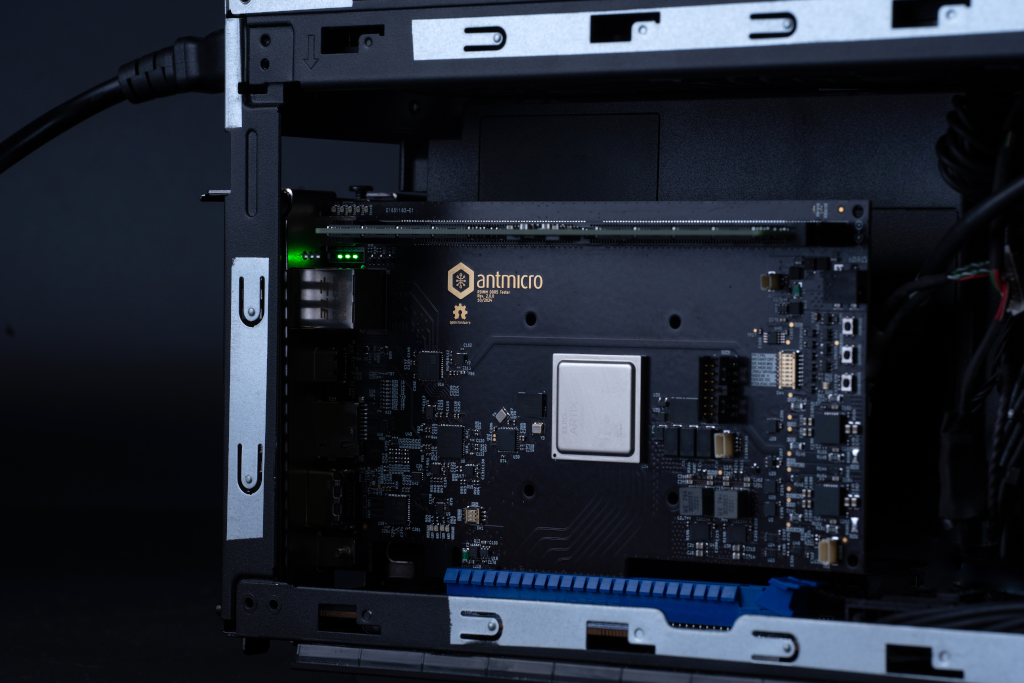

The selected hardware platforms used for DRAM testing include an optional PCIe interface break-routed from the on-board FPGA. These platforms are SO-DIMM DDR5 Testers supporting PCIe x4 and RDIMM DDR5 Tester in Revision 2.0 supporting PCIe x8. The platforms were designed in the form factor of PCIe cards and are mechanically compliant with host platforms with a PCIe root complex.

Fig. 23 RDIMM DDR5 Tester connected to Intel NUC-series host PC over PCIe x8.¶

Enabling a PCIe interface in the digital design allows for fast data exchange between the host PC, the FPGA and the memory.

Note

Enabling PCIe connectivity currently requires extending the existing the Rowhammer tester codebase with setup-specific features. In particular, PCIe requires mapping the API/commands into a Rowhammer-specific API.

DRAM Bender integration¶

PCIe interface allows to integrate the RDIMM DDR5 Tester with third party DRAM testers. One of them is DRAM Bender project. In order to make the RDIMM DDR5 Tester compliant with DRAM Bender API it is required to transpile Bender API into Rowhammer Payload Executor command set via an intermediate software layer. The software layer executed on the PCIe host side can map the 3rd-party command set into Rowhammer Tester format with respect to the mapping specified below.

The table below presents encodings for the supported Payload Executor instructions.

The NOOP, LOOP and STOP instructions are used to control the flow of the Payload Executor module (are not propagated to the memory).

The DFI instruction is a sequence of the DDR commands and its length is determined by the number of preconfigured DDR phases. The example below presents single Rowhammer Tester instruction for the device working in 4 phases.

This mapping is common for all DRAM variants, the LSB distinguishes the Payload Executor control commands from the DFI commands.

After having transpilled the program, it is expected for the driver to transfer the the payload over the PCIe interface onto the Rowhammer Tester platform.

| INSTRUCTION | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32-39 | 40-63 | 64-71 | 72-95 | 96-103 | 104-127 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| STOP | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | X | X | X | X | X | X |

| NOOP | 1 | 0 | 0 | 0 | NOOP TIMESLICE | X | X | X | X | X | X | |||||||||||||||||||||||||||

| LOOP | 1 | 0 | 0 | 1 | LOOP COUNT | LOOP JUMP | X | X | X | X | X | X | ||||||||||||||||||||||||||

| DFI | 0 | TIMESLICE | DFI PHASE 0 | X | DFI PHASE 1 | X | DFI PHASE 2 | X | DFI PHASE 3 | |||||||||||||||||||||||||||||

The table below represents the DDR-specific instructions encoding for the Rowhammer Tester platform.

A row of the table represents the DDR command (if one-cycle) or a DFI PHASE of the command.

Each of the DDR command in the DFI sequence can be prefixed with a TIMESLICE argument that determines the delay with which the next command in sequence is issued.

| Bit number | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Signal | CS_n | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 | CA6 | CA7 | CA8 | CA9 | CA10 | CA11 | CA12 | CA13 | RFU | ||||||||

| ACT | 0 | 0 | 0 | R0 | R1 | R2 | R3 | BA0 | BA1 | BG0 | BG1 | BG2 | CID0 | CID1 | CID2 | X | X | X | X | X | X | X | X | X |

| 1 | R4 | R5 | R6 | R7 | R8 | R9 | R10 | R11 | R12 | R13 | R14 | R15 | R16 | CID3/R17 | X | X | X | X | X | X | X | X | X | |

| PREpb | 0 | 1 | 1 | 0 | 1 | 1 | CID3 | BA0 | BA1 | BG0 | BG1 | BG2 | CID0 | CID1 | CID2 | X | X | X | X | X | X | X | X | X |

| REFab | 0 | 1 | 1 | 0 | 0 | 1 | CID3 | X | X | 1 | 1 | 0 | CID0 | CID1 | CID2 | X | X | X | X | X | X | X | X | X |

| ZQCal Start (MPC) | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | X | X | X | X | X | X | X | X | X | X |

| ZQCal Latch (MPC) | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | X | X | X | X | X | X | X | X | X | X |

| RD | 0 | 1 | 0 | 1 | 1 | 1 | 0 | BA0 | BA1 | BG0 | BG1 | BG2 | CID0 | CID1 | CID2 | X | X | X | X | X | X | X | X | X |

| 1 | C2 | C3 | C4 | C5 | C6 | C7 | C8 | C9 | C10 | X | 1 | X | X | CID3 | X | X | X | X | X | X | X | X | X | |

| RDA | 0 | 1 | 0 | 1 | 1 | 1 | 0 | BA0 | BA1 | BG0 | BG1 | BG2 | CID0 | CID1 | CID2 | X | X | X | X | X | X | X | X | X |

| 1 | C2 | C3 | C4 | C5 | C6 | C7 | C8 | C9 | C10 | X | 0 | X | X | CID3 | X | X | X | X | X | X | X | X | X | |

| WR | 0 | 1 | 0 | 1 | 1 | 0 | 0 | BA0 | BA1 | BG0 | BG1 | BG2 | CID0 | CID1 | CID2 | X | X | X | X | X | X | X | X | X |

| 1 | X | C3 | C4 | C5 | C6 | C7 | C8 | C9 | C10 | X | 1 | 0 | X | CID3 | X | X | X | X | X | X | X | X | X | |

| WRA | 0 | 1 | 0 | 1 | 1 | 0 | 0 | BA0 | BA1 | BG0 | BG1 | BG2 | CID0 | CID1 | CID2 | X | X | X | X | X | X | X | X | X |

| 1 | X | C3 | C4 | C5 | C6 | C7 | C8 | C9 | C10 | X | 0 | 0 | X | CID3 | X | X | X | X | X | X | X | X | X | |

| Bit number | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Signal | CS_n | ACT_n | A0 | A1 | A2 | A3 | A4 | A5 | A6 | A7 | A8 | A9 | A10/AP | A11 | A12/BC_n | A13 | A14/WE_n | A15/CAS_n | A16/RAS_n | A17 | BA0 | BA1 | BG0 | BG1 |

| ACT | 0 | 0 | RA0 | RA1 | RA2 | RA3 | RA4 | RA5 | RA6 | RA7 | RA8 | RA9 | RA10 | RA11 | RA12 | RA13 | RA14 | RA15 | RA16 | RA17 | BA0 | BA1 | BG0 | BG1 |

| PRE | 0 | 1 | X | X | X | X | X | X | X | X | X | X | 0 | X | X | X | 0 | 1 | 0 | X | BA0 | BA1 | BG0 | BG1 |

| PREA | 0 | 1 | X | X | X | X | X | X | X | X | X | X | 1 | X | X | X | 0 | 1 | 0 | X | X | X | X | X |

| REF | 0 | 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 1 | 0 | 0 | X | X | X | X | X |

| ZQCS | 0 | 1 | X | X | X | X | X | X | X | X | X | X | 0 | X | X | X | 0 | 1 | 1 | X | X | X | X | X |

| ZQCL | 0 | 1 | X | X | X | X | X | X | X | X | X | X | 1 | X | X | X | 0 | 1 | 1 | X | X | X | X | X |

| RD | 0 | 1 | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 | CA6 | CA7 | CA8 | CA9 | 0 | X | X | X | 1 | 0 | 1 | X | BA0 | BA1 | BG0 | BG1 |

| RDA | 0 | 1 | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 | CA6 | CA7 | CA8 | CA9 | 1 | X | X | X | 1 | 0 | 1 | X | BA0 | BA1 | BG0 | BG1 |

| WR | 0 | 1 | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 | CA6 | CA7 | CA8 | CA9 | 0 | X | X | X | 0 | 0 | 1 | X | BA0 | BA1 | BG0 | BG1 |

| WRA | 0 | 1 | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 | CA6 | CA7 | CA8 | CA9 | 1 | X | X | X | 0 | 0 | 1 | X | BA0 | BA1 | BG0 | BG1 |

| Bit number | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Signal | CS | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 | CA6 | CA7 | CA8 | CA9 | CA10 | CA11 | CA12 | CA13 | RFU | ||||||||

| ACT-1 | 1 | 1 | 1 | 1 | R14 | R15 | R16 | R17 | BA0 | BA1 | BG0/BA2 | BG1/BA3/X | R11 | R12 | R13 | X | X | X | X | X | X | X | X | X |

| ACT-2 | 1 | 1 | 1 | 0 | R7 | R8 | R9 | R10 | R0 | R1 | R2 | R3 | R4 | R5 | R6 | X | X | X | X | X | X | X | X | X |

| PRE | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | BA0 | BA1 | BG0/BA2 | BG1/BA3/X | X | X | 0 | X | X | X | X | X | X | X | X | X |

| PREA | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | BA0 | BA1 | BG0/BA2 | BG1/BA3/X | X | X | 1 | X | X | X | X | X | X | X | X | X |

| REF | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | BA0 | BA1 | BG0/BA2 | RFM | SB0/X | SB1/X | 0 | X | X | X | X | X | X | X | X | X |

| REFA | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | BA0 | BA1 | BG0/BA2 | RFM | SB0/X | SB1/X | 1 | X | X | X | X | X | X | X | X | X |

| ZQ CAL Start (MPC) | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | X | X | X | X | X | X | X | X | X |

| ZQ CAL Latch (MPC) | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | X | X | X | X | X | X | X | X | X |

| RD/RD16 | 1 | 1 | 0 | 0 | C0 | C3 | C4 | C5 | BA0 | BA1 | BG0/BA2 | BG1/BA3/B4 | C1 | C2 | AP | X | X | X | X | X | X | X | X | X |

| RD32 | 1 | 1 | 0 | 1 | C0 | C3 | C4 | C5 | BA0 | BA1 | BG0/BA2 | BG1/BA3 | C1 | C2 | AP | X | X | X | X | X | X | X | X | X |

| WR/WR16 | 1 | 0 | 1 | 1 | C0 | C3 | C4 | C5 | BA0 | BA1 | BG0/BA2 | BG1/BA3/X | C1 | C2 | AP | X | X | X | X | X | X | X | X | X |

| WR32 | 1 | 0 | 0 | 1 | 0 | C3 | C4 | C5 | BA0 | BA1 | BG0/BA2 | BG1/BA3 | C1 | C2 | AP | X | X | X | X | X | X | X | X | X |

| Bit number | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Signal | CS | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 | RFU | ||||||||||||||||

| ACT-1 | 1 | 1 | 0 | R12 | R13 | R14 | R15 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 0 | BA0 | BA1 | BA2 | R16 | R10 | R11 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | |

| ACT-2 | 1 | R17 | R18 | R6 | R7 | R8 | R9 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 0 | R0 | R1 | R2 | R3 | R4 | R5 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | |

| PRE | 1 | 0 | 0 | 0 | 0 | 1 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 0 | BA0 | BA1 | BA2 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | |

| REF | 1 | 0 | 0 | 0 | 1 | 0 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 0 | BA0 | BA1 | BA2 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | |

| ZQCal Start (MPC) | 1 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | |

| ZQCal Latch (MPC) | 1 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | |

| RD-1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 0 | BA0 | BA1 | BA2 | X | C9 | AP | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | |

| WR-1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 0 | BA0 | BA1 | BA2 | X | C9 | AP | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | |